受注案件7369件(2026年3月末時点)の実績

「ソフテックだより」では、ソフトウェア開発に関する情報や開発現場における社員の取り組みなどを定期的にお知らせしています。

さまざまなテーマを取り上げていますので、他のソフテックだよりも、ぜひご覧下さい。

ソフテックだより(発行日順)のページへ

ソフテックだより 技術レポート(技術分野別)のページへ

ソフテックだより 現場の声(シーン別)のページへ

「ソフテックだより」では、みなさまのご意見・ご感想を募集しています。ぜひみなさまの声をお聞かせください。

私は本社事業所勤務の主に組み込み系のソフトウェア開発を担当している社員です。数年前に入社20年の節目を迎え、周りを見渡すといつの間にかベテラン社員になってしまいました。

最近、シリアルフラッシュメモリ(Serial Flash Memory)を使用したブートプログラムの開発を行う機会がありましたので、その内容と注意点などについてご紹介したいと思います。

シリアルフラッシュメモリについては、過去のソフテックだより第437号技術レポート「シリアルフラッシュメモリを利用するポイント」でご紹介しています。

シリアルフラッシュメモリを利用するメリットとして、以下のような点があげられます。

今回ご紹介するブートプログラムですが、ルネサスエレクトロニクス社のRZ/AシリーズCPUを使用して開発しています。RZ/Aシリーズは、3点目にあげたシリアルフラッシュメモリからのブートモードを備えているほか、周辺機能であるSPIマルチI/Oバスコントローラの「外部アドレス空間リードモード」を使用することで、シリアルフラッシュメモリを制御するためのSPI通信コマンドを意識することなく、データの読み出しが可能となっています。

組み込みソフトのブートプログラムについては、過去のソフテックだより第41号技術レポート「V850の特性を利用した二重構造のIPLプログラム開発」でご紹介しています。こちらでご紹介したブートプログラムは、V850 CPUのブートスワップ機能を使用して、プログラムを二面(ブロック0、ブロック1)持たせることで、不測の事態により書き換えに失敗した場合でも、起動不能にならないような仕組みを実現していました。

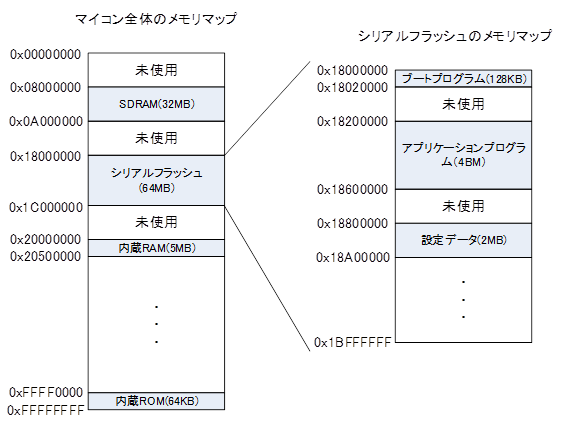

今回ご紹介するシステム(下図メモリマップ参照)では、プログラムや設定データをシリアルフラッシュメモリに格納し、シリアルフラッシュメモリからブートさせる必要がありました。シリアルフラッシュメモリおよびRZ/AシリーズCPUには、ブートスワップ機能がありませんので、ブートプログラムとアプリケーションプログラムを分けて格納し、製品ソフトの更新はアプリケーションプログラムのみで行うことにしました。この場合、アプリケーションプログラムの更新に一度失敗しても、ブートプログラムが消えない限り、再度書き換えが可能です。

図1. メモリマップ(イメージ)

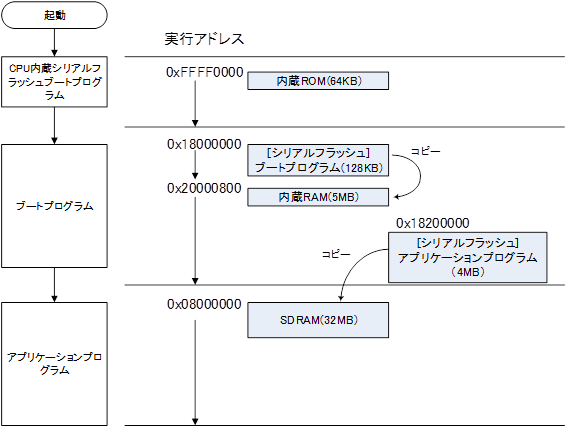

また、プログラム実行速度を少しでも速めたいため、ブートプログラム、アプリケーションプログラムともにRAM上にコピーして動作させています。RAM上で動作させることにより、シリアルフラッシュの書き換え(ブートプログラム内でのアプリケーションプログラムの更新、アプリケーションプログラム内での設定データの更新)が任意のタイミングで実行できます。

前述の通り、RZ/AシリーズCPUは、シリアルフラッシュメモリからのブートモードを備えており、起動すると、内蔵ROM(変更不可)に格納されたCPU内蔵シリアルフラッシュブートプログラムが実行されます。

起動からアプリケーションプログラムが実行されるまでの流れを下図に示します。

図2. 実行プログラムの流れ

図に示した通り、CPU内蔵シリアルフラッシュブートプログラム、ブートプログラム、アプリケーションプログラムの順に処理が実行されます。各プログラムで実行されるシリアルフラッシュに関連する主な処理内容について、以下に示します。なお、システムクロックの設定やベクタアドレスの設定、MMU(メモリマネジメントユニット)の設定など、RZ/AシリーズCPU起動に必須の初期設定の説明は、ここでは省略しています。

[CPU内蔵シリアルフラッシュブートプログラムの処理]

[ブートプログラムの処理]

アプリケーションプログラムの処理については割愛しますが、以上の処理で、シリアルフラッシュに格納したアプリケーションプログラムをSDRAMにコピーし、SDRAM上で実行することができます。

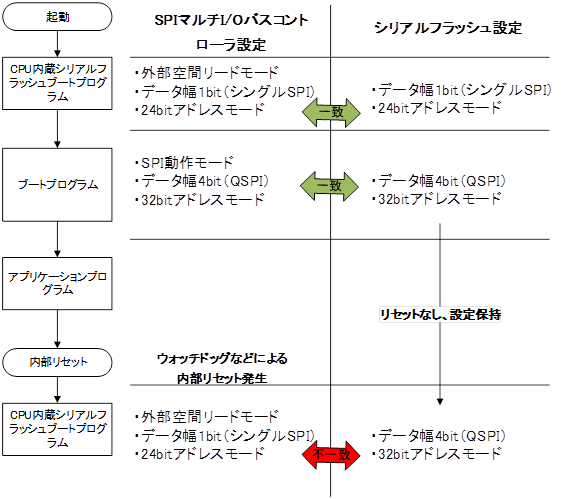

前項でアプリケーションプログラムを実行する方法について説明しましたが、アプリケーションプログラム実行後の処理に関して、ひとつ注意点があります。

アプリケーション内でウォッチドッグタイマなどによるCPU内部リセットが発生した場合、シリアルフラッシュも同時にリセットさせなければ、シリアルフラッシュからブートプログラムを読み出せず、起動できなくなるケースがあります(下図参照)。これは、内部リセットでCPUが再起動した際のSPIマルチI/Oバスコントローラとシリアルフラッシュのデータ幅、アドレスモードなどの不一致が原因です。

図3. CPU内部リセットで再起動できなくなるケース

この問題を回避するには、回路設計段階で内部リセット発生時にシリアルフラッシュを確実にリセットさせる設計上の考慮が必要になります。具体的な対策としては、ウォッチドッグタイマがオーバーフローしたときに出力されるWDTOVF#信号をシリアルフラッシュのRESET#端子に接続するなどになります。

今回は、シリアルフラッシュブートプログラムの開発についてご紹介しました。シリアルフラッシュメモリは、省配線など基板設計上のメリットが大きく、小型化が求められる組み込み機器においては、今後も更なる普及が見込まれるデバイスであると思います。今号が皆様のソフト開発のお役にたちましたら幸いです。

最後までお読みいただきありがとうございました。

(T.S.)

関連ページへのリンク

関連するソフテックだより

「ソフテックだより」では、みなさまのご意見・ご感想を募集しています。ぜひみなさまの声をお聞かせください。